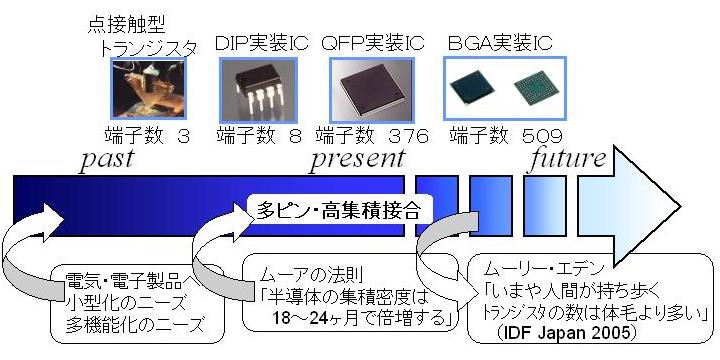

電気・電子製品にはこれまで,小型化のニーズがありました.そのため,その内部で使われる電子デバイスを小型化する必要がありました.また,同時に高性能化のニーズもあったため,電子デバイス中のトランジスタを増やさねばなりませんでした.結果電子デバイスは高度に高密度化・高集積化しました.この高集積化そのものにデバイスの性能をあげる効果があったことが,デバイスの高密度化をさらに加速しました.デバイスに使われるトランジスタが増えれば,デバイスの端子数も増やさねばなりません.そこで,増加する端子数に対応するためDIP(Dual In-line Package),QFP(Quad Flat Package),BGA(Ball Grid Array)と,より高密度な実装技術が次々に開発されました.

キーボードやボタンのような入力デバイス,ディスプレイのような出力デバイスには最低限必要なサイズがありますから,電気・電子製品に対する小型化のニーズには歯止めがかかりつつありますが,むしろ多機能化の流れは加速しています.また,トランジスタの平面密度には物理的限界がありますが,MCM(Multi-Chip Module)やSiP(System in Package)のようにデバイスあたりのトランジスタ数を増やす手段が講じられる一方で,BGAをはじめとするグリッドアレイ実装法以降,より高密度な実装を実現する有力な提案はなされていません.実装の多ピン化・狭ピッチ化はこれからも進めざるを得ないのです.

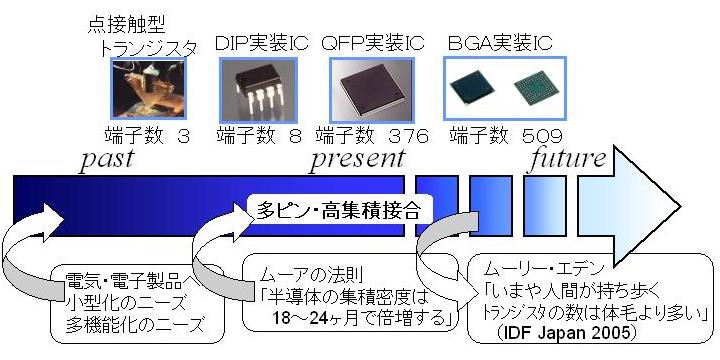

現在最も良く用いられている高密度実装法は上段のソルダバンプ接合法です.これは高信頼性の導通路を形成できる一方で,工程数が多く,その工程にそれぞれ固有の設備が必要な点で高コストな実装といえます.また,信頼性を高めるためには高精度な観察が必要なことも,コストを高める一因となっています.下段の導電性接着剤による接合法は低コストな一方で,フィラー間・フィラー−ランド間に周囲の絶縁性樹脂が侵入することで導電性が経時的に変化する,すなわち信頼性が低いことが知られています.今,高密度かつ高信頼性の導通路を低コストに形成する実装法が求められているのです.

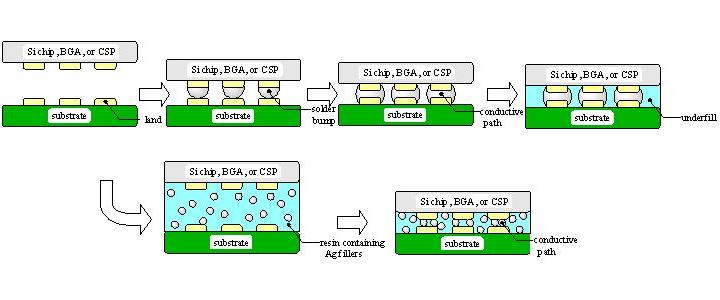

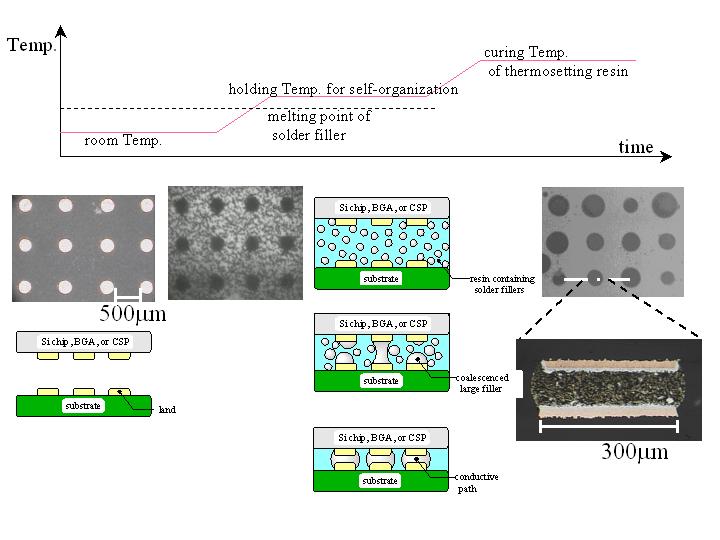

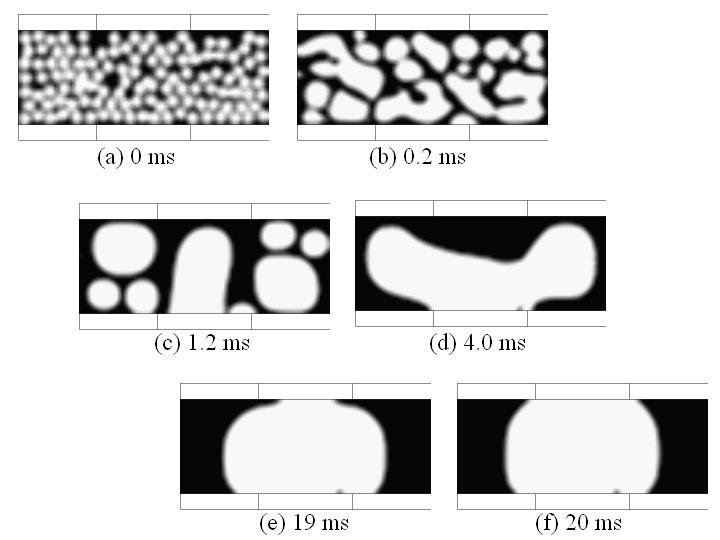

エリアアレイ状に銅ランドを形成したデバイスと基板との間に,ソルダフィラーを含有した熱硬化性樹脂をはさみます.当初フィラーは樹脂中に均等分散していますが,フィラーの融点以上の温度に加熱・保持すると,フィラー同士が合体していきます.こうして合体が進むうち,フィラーの中にはデバイスや基板にぬれるものが現れますが,それらはよりぬれやすいランド上に輸送されます.この輸送によってさらにフィラーの合体が促され,ついには対向ランド間に導通路を自己組織化します.この自己組織化実装法を用いれば,導電性接着剤を用いるのと同様の設備を用いて低コストに,ソルダバンプ実装法と同様の高信頼性な導通路を形成できる可能性があります.

この自己組織化実装プロセスのうち,フィラー融点以上の温度保持過程を2相流流体解析によってシミュレーションすることができました.これによって,時間的・空間的にスケールが小さく観察の難しかったフィラーの自己組織化現象を可視化することができました.この結果から現象の支配因子が明らかになりつつあります.

自己組織化現象を利用しているため,デバイスや基板の設計が変更されたときにも実装技術者は設備やプログラムを変更する必要がありません.また,導通路周囲の樹脂が接合部の強度を担うため,ソルダバンプ実装法に比べ導通路材料の選択が自由で,低温接合にも対応できます.

また,多デバイス同時接続によるさらなる低コスト化の効果も期待できます.